【設計者必見】その直列接続、危険です。ISO 14119:2024が警鐘を鳴らす「フォールトマスキング」の罠とPL低下のメカニズム

ジュンイチロウ

ジュンイチロウこんにちは ジュンイチロウです!

機械の安全設計、特にCEマーキング対応で、「これで本当に大丈夫だろうか?」と悩んだ経験はありませんか?

私は普段、様々な現場で安全設計のコンサルティングをしていますが、特に「フォールトマスキング」に関する課題に頻繁に出会います。非常に多くの方が「以前、別のコンサルタントや認証機関からはOKと言われたのですが…」とおっしゃいます。

良かれと思って構築した安全関連回路が、意図せず危険な状態を隠してしまっている。こうした状況は、設計者にとっても、そして機械の使用者にとっても、決して望ましいものではありません。

この記事では、初心者の方には少し難しく感じるかもしれませんが、安全設計の要となる ISO 14119:2024 の考え方に基づき、「フォールトマスキング」の正しい理解と対策について、分かりやすく解説していきます。そこで今回は、一部の初学者の方には少し難しい内容かもしれませんが、ISO 14119 が示す「フォールトマスキング」の考え方と、現場で実践できる対策のヒントを発信します。

目次

序論:フォールトマスキングという重大なパラドックス

フォールトマスキング (fault masking) とは

制御システムの安全関連部分(SRP/CS)の故障のない部分の動作により、安全関連部分 (SRP/CS) の故障が意図せずにリセットされたり、故障の検出が妨げられたりすること。

一般的なシナリオとそこに潜む脆弱性

多数の安全扉を持つ複雑な自動生産ラインを想像してみてください。経済性や配線の簡素化のため、これらの扉のインターロック装置は、しばしば「デイジーチェーン」と呼ばれる直列接続で、単一のセーフティリレーや安全PLCの入力に接続されます。この一見効率的に見える一般的な手法は、深刻かつ誤解されがちな脆弱性、すなわち「フォールトマスキング」を内包しています。

デイジーチェーン(英: daisy chain)は、複数の電気・電子機器を数珠つなぎにする、あるいは全部まとめて1つの輪にするような接続方法である

https://ja.wikipedia.org/wiki/%E3%83%87%E3%82%A4%E3%82%B8%E3%83%BC%E3%83%81%E3%82%A7%E3%83%BC%E3%83%B3

パラドックスの定義:機能安全と高可用性の思想的対立

この問題を深く理解するためには、まず「フォールトマスキング」という用語が持つ二面性、すなわち設計思想の根本的な違いから生じるパラドックスを解き明かす必要があります。

- 高可用性IT/コンピューティングにおける思想高可用性が求められるITシステムの世界では、フォールトマスキングはフォールトトレラントシステムが持つべき望ましい特性とされます。これは、システムの一部に障害が発生しても、冗長化された他の部分が処理をシームレスに引き継ぎ、エンドユーザーからはその障害が「隠蔽(マスク)」されることで、システムの継続的な稼働と可用性を維持する技術を指します。ここでの至上命題は、サービスの継続性です。

- 機能安全における思想対照的に、機械の機能安全の分野において、フォールトマスキングは危険で望ましくない現象です。ISO 14119では、「故障の意図しないリセット、または制御システムの安全関連部における故障の検出を妨げること」と明確に定義されています。機能安全の第一目標は、いかなる犠牲を払ってでも稼働を続けることではなく、故障が発生した際に確実に安全な状態へ移行することです。故障を隠蔽することは、この安全な状態への移行を妨げ、潜在的で危険な状態を作り出すことに他なりません。

フォールトマスキングは相反する2つの性質をもちます!

この記事の目標

この記事では、機能安全におけるフォールトマスキングの概念を解剖し、それが機械の安全レベル計算に与える深刻な影響を明らかにします。さらに、2024年に改訂されたISO 14119 の附属書J が規定する評価手法について実用的なガイドを提供し、このリスクを排除するために必要な技術的解決策を詳述します。

この言及の出発点として、IT分野と機能安全分野における「フォールトマスキング」という用語の思想的衝突を理解することは極めて重要です。IT分野の技術者がこの用語を聞けば、堅牢な冗長システムを想起するかもしれません。しかし、ISO 13849-1 やISO 14119 の文脈では、この用語は診断機能の失敗(故障)を意味します。稼働時間(ミッションタイム)を優先するか、安全状態への移行を優先するかという、この根本的な思想の違いこそが、この問題の危険性の根源です。本稿はこの曖昧さを解消し、機械の安全性を最優先する明確なフレームワークを構築することから始めます。

マスクされた故障の解剖学:安全システムはいかにして騙されるか

基礎:無電圧接点の直列接続

まず明確にすべきは、ISO 14119 附属書J で言及されるフォールトマスキング問題が、特に単純な機械式の無電圧接点(ポテンシャルフリー接点、または「ドライ接点」とも呼ばれる)を持つインターロック装置の直列接続に適用されるということです。これらの装置は、自己監視機能を内蔵していません。

メカニズム1:直接的なフォールトマスキング(ISO 14119, 図J.7 に基づく図解)

2つの扉を持つ機械を例に、段階的なシナリオで解説します。

STEP

正常運転

扉A1とA2は閉じています。2チャンネルの安全回路は導通しており、セーフティリレーは機械の運転を許可しています。

STEP

故障発生

扉A1のインターロック装置に故障F1が発生します(例:片方のチャンネルの短絡や接点溶着)。扉は閉じたままであるため、この故障は潜在的なまま検出されません。

STEP

故障検出の試み

扉A2が開かれます。セーフティリレーは2つのチャンネル間の不一致を検出します(一方は開路、もう一方は故障により閉路のまま)。これにより、システムは正しく故障状態に入り、再起動を阻止します。

STEP

マスキング行為

扉A1が開かれ、システムが故障状態にある間に、作業者が扉A2を開閉します。セーフティリレーは、自身の入力チャンネルが両方とも開路(A2が開いた時)になり、その後両方とも閉路(A2が閉じた時)になるのを観測します。リレーの観点からは、この有効な開閉サイクルは、故障していないスイッチの正当なシステムサイクルとして解釈され、自身の故障状態を「リセット」してしまいます。

STEP

危険な結果

扉A1の故障F1は今やマスクされた状態にあります。システムには危険な故障が依然として存在するにもかかわらず、セーフティリレーは再起動準備が整ったと判断します。次に別の故障が発生すれば、安全機能の完全な喪失につながる可能性があります。

メカニズム2:意図しない故障のリセット(ISO 14119, 図J.8, J.9 に基づく図解)

これは、別の装置を操作する行為そのものが、検出された故障をロジックユニットのメモリから消去してしまう、という関連性の高いシナリオです。セーフティリレーやセーフティーコントローラーのような監視ロジックユニットによって検出された故障が、後続の故障していないガードの操作によって意図せずリセットされ、システムが元の故障は修復されたと誤認する仕組みを解説します。これは特に、図J.9 に示されるような配線における故障で顕著となります。

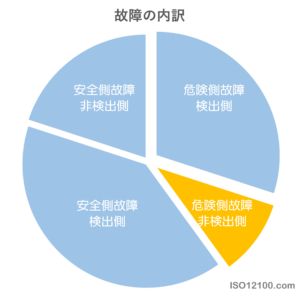

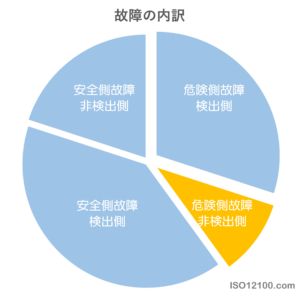

重大な結果:診断カバレッジ(DC)とパフォーマンスレベル(PL)の低下

故障の連鎖

このセクションでは、フォールトマスキングが、計算された安全システムをいかにして不適合なものへと変えてしまうのか、その直接的な因果関係を明らかにします。フォールトマスキングは単なる軽微な不具合ではありません。それは、システムの安全インテグリティを体系的に破壊するドミノ倒しの最初の牌です。

フォールトマスキングによってDC が下がるということです!

- 直列接続されたスイッチで故障が発生します。

- 別のスイッチの操作がこの故障をマスクします 。

- マスクされた故障は、定義上、未検出の危険側故障となります。

- システムの故障検出能力は、ISO 13849-1 で定義される診断カバレッジ(DC) によって定量化されます 。

- したがって、フォールトマスキングの可能性は、システムの実際のDCを直接的に低下させます。

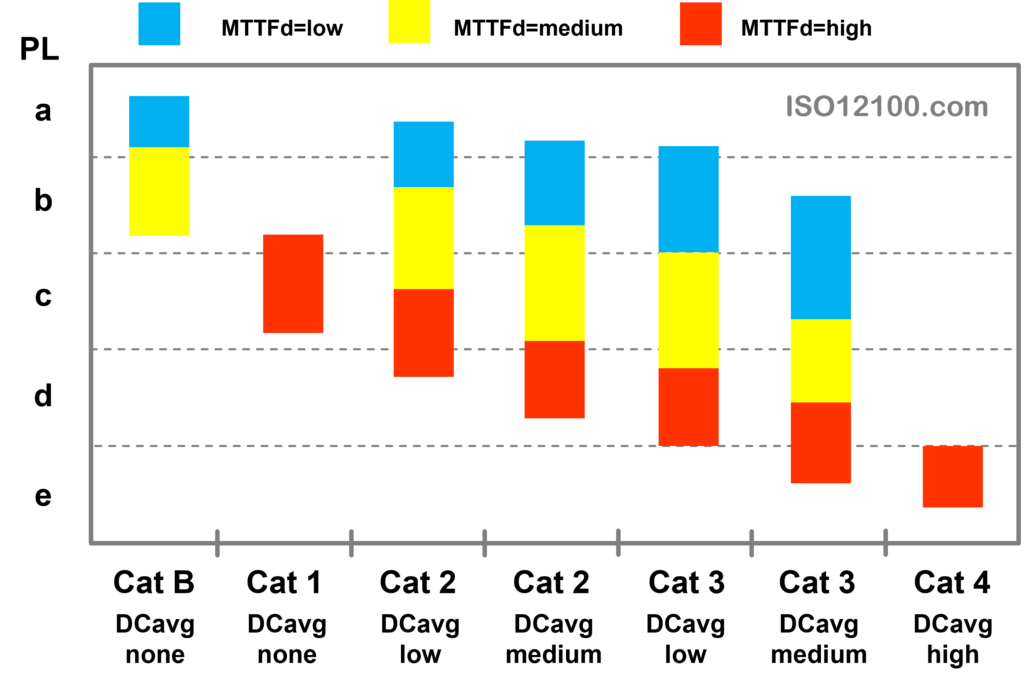

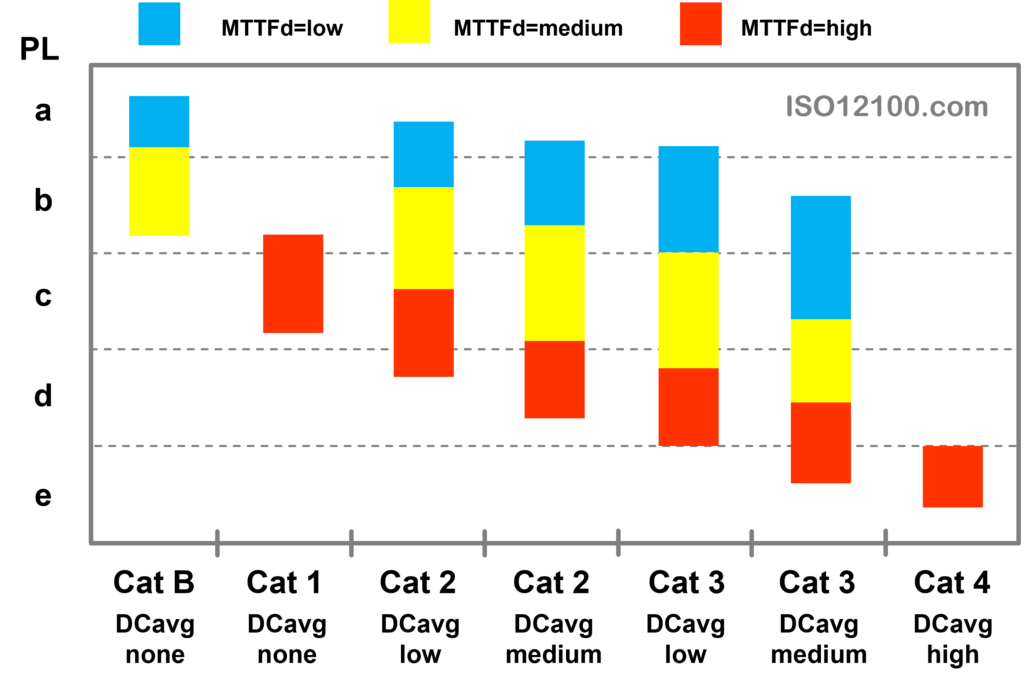

- ISO 13849-1 の基本原則によれば、達成可能なパフォーマンスレベル(PL) は、カテゴリ、MTTFᴅ(平均危険側故障時間)、およびDC の関数です。

- たとえ信頼性の高い部品(高いMTTFᴅ)を使用していても、DC が低下すれば、達成可能なPL も低下します。

- 結論: 設計者は、部品データに基づいてシステムが PLd を満たすと計算したかもしれません。しかし、フォールトマスキングの存在により、実際に達成可能な PL は PLc かそれ以下にまで低下し、結果として要求されるリスク低減 PLr を満たせず、見せかけだけの安全な機械を生み出してしまうのです。

あわせて読みたい

PL決定に役立つ安全機能の故障検出能力の自己診断率DCとSRP/CSへの平均自己診断率DCavgの計算方法

あらすじ こんにちは! 今日はISO13849-1 の平均自己診断率(DCavg) とは簡単にいうとどういうことでしょう?というテーマでお話ししたいと思います。 DCavg とは、安全…

ISO 13849-1, 図12 を用いた影響の可視化

この影響を視覚的に理解するために、ISO 13849-1 のPLチャート(図12)が中心的な役割を果たします。

診断カバレッジ(DC) の導入

診断カバレッジ(DC) を簡単に言えば、「システムが自身の故障を見つけるのがどれくらい得意か?」という指標です。 ISO 13849-1:2023 の3.1.35 項 では、より正式に「全危険側故障率に対する、検出された危険側故障率の比として決定される、診断の有効性の尺度」と定義されています 。

スクロールできます

| レベル | DC値 | 意味 |

| High 高 | DC≥99% | システムは実質的に全ての危険側故障を検出する。 |

| Middle 中 | 90%≤DC<99% | システムはほとんどの危険側故障を検出する。 |

| Low 低 | 60%≤DC<90% | システムは過半数の危険側故障を検出する。 |

| None なし | DC<60% | システムには信頼できる故障検出能力がほとんどない。 |

マスキングがDC をいかに破壊するか

例えば、高信頼性の部品を用いたカテゴリ3 のシステムを設計するケースを考えます。設計者は、セーフティリレーがチャンネル間の不一致を検出できるため、高いDC(例:99%)を想定します。この組み合わせは、チャート上ではPLd やPLe を指し示します。

しかし、ここでフォールトマスキングの影響を考慮に入れます。

これは、フォールトマスキングが最終的な安全評価にいかに壊滅的な影響を与えるかを明確に物語っています。

無電圧接点を直列つなぎにすればするほどDCが下がり、結局PLを満たさないということです!

見えないリスクの定量化:ISO 14119:2024 附属書J 実践ガイド

附属書J の概要

附属書J は、直列接続された無電圧接点装置を使用する際に、フォールトマスキングがDC に与える影響を評価するための、規格的(準拠が必須の)枠組みを提供します。

簡易手法による最大達成可能DC 表J.1

この手法は、迅速かつ保守的な評価を提供し、一次的な分析ツールとして位置づけられます。表J.1 のロジックを分解し、その背後にある統計的推論を解説します。

スクロールできます

| 頻繁に使用される可動ガードの数 a), b) | その他の可動ガードの数 c) | 最大達成可能DC d) |

| 0 | 2~4 | Medium |

| 5~30 | Low | |

| >30 | None | |

| 1 | 1 | Medium |

| 2~4 | Low | |

| ≧5 | None | |

| >1 | ≧0 | None |

a) 「頻繁に使用される可動ガードの数」(1時間に1回以上): これが故障確率の主要な駆動要因であると説明されます。作動回数が多いほど、コンポーネントが故障し、その故障がマスクされる機会が増えます。

b)「その他の可動ガードの数」: 「マスキング事象」の潜在的な数を増加させる要因として説明されます

c) 「オペレーターの数」: マスキング確率の乗数として機能します。複数の作業者がいることで、故障を隠蔽しうる同時またはほぼ同時の作動の可能性が高まるためです

d) 「予見可能なマスキング」:もしマスキングが通常の操作(例:ある作業のために常に2つの扉を開ける)の一部として予見される場合、DCは「None」となります。これは、交渉の余地のない設計上の制約として強調されるべき重要な点です。

通常手法 表J.2, J.3

この手法は、簡易手法が厳しすぎる場合に、より詳細な分析を行うためのものです。プロセスは明確なステップに分けられます。

ステップ1 フォールトマスキング確率 (FM) レベルの決定(表J.2)

表J.2 を用いて、同じ要因(頻度、オペレーター数など)から FMレベル(1, 2, または3)を導き出す方法を解説します。このステップは、マスキング事象の発生しやすさを定量化します。

このステップでは、システムの運用状況をより詳細に分析し、フォールトマスキングが発生する確率を「FMレベル」として定量化します。表J.2 は、簡易手法と同様のパラメータ(作動頻度、オペレーター数など)を用いて、マスキングが発生する確率をより詳細な「FMレベル」(1, 2, 3)として導き出します。レベル1 が最も確率が低く、レベル3 が最も高くなります。

| 頻繁に使用される可動ガードの数 a), b) | その他の可動ガードの数 c) | フォールトマスキング確率レベル (FM) d) |

| 0 | 2~4 | 1 |

| 5~30 | 2 | |

| >30 | 3 | |

| 1 | 1 | 1 |

| 2~4 | 2 | |

| ≧5 | 3 | |

| >1 | ≧0 | 3 |

a) 作動頻度が1時間に1回を超える場合

b) 複数のオペレーターが別々のガードを開けることができる場合、頻繁に使用される可動ガードの数を1つ増やします

c) ガード間の最小距離が5m を超える場合、またはオペレーターが頻繁に使用するガードを操作する位置から他のガードに直接手が届かない場合、この数を1段階減らすことができます

d) 通常の操作やサービスの一環として複数のガードが同時に開くなど、故障マスキングが予見される場合、FMレベルは3になります

ステップ2 最大達成可能DC の決定(表J.3)

これが通常手法の核心です。FMレベルを、システムの設計に基づいた固有の診断能力と結びつけます。システムのアーキテクチャこそが、その診断能力を決定づけます。最大達成可能DC は、単にセーフティリレーの性能だけで決まるのではなく、現場の配線からコントローラ内の信号処理に至るまで、システム全体のアーキテクチャに依存する包括的な特性なのです。

配線(スター vs. ブランチ/トランク vs. ループ)

スター配線は、故障が単一の配線に分離されるため、最良の診断ポテンシャルを提供します。ループ配線やブランチ/トランク配線は、単一の配線故障(例:電源への短絡)が複数の装置に影響を与える可能性のある共通経路を作り出し、診断を困難にします。

信号評価(静的 vs. 動的)

静的な 0V/24V レベルのみをチェックするロジックユニットは容易に騙されます。動的信号(例:テストパルス)を使用するユニットは、回路の電気的完全性(短絡、断線)を能動的に調査しており、静的監視では見逃される故障を検出できます。これはより堅牢な診断方法です。

配置(単一 vs. 冗長)

2つの独立したインターロック装置を使用する(冗長配置)ことは、単一装置の2接点を使用する(単一配置)よりも、物理的な分離が大きく、共通原因故障を低減するため、より多くの診断可能性を提供します。

比較深掘り:表J.3, J.4, J.5 の具体的仕様

このセクションでは、3つの表を個別に提示し、その違いと背景にある論理を詳細に分析します。これらの表の根本的な違いは、配線(ケーブル)の物理的な設置状況に起因する故障モードのリスク階層を反映している点にあります。

表J.3:ベースライン – 保護されていないケーブル、電源線なし

表J.3 供給電圧(UN)線なしの非保護多芯ケーブルで最大達成可能なDC

| FMレベル | 信号評価 |

| 同極性 | |

| 1 | Low |

| 2 | None |

| 3 | None |

分析: この表は、最も一般的でありながら脆弱な配線シナリオを対象としています。ケーブルが機械的な保護を受けておらず、かつ安全信号線以外の電源線(UN) がケーブル内に含まれていない場合です。FMレベル(マスキングの確率)が上がるにつれて、達成可能なDC 低下することが明確にわかります。また、信号評価技術に注目すると、「動的信号」が常に最も高いDC を達成できる可能性を示しています。

表J.4:リスクの増大 – 保護されていないケーブル、電源線あり

表J.4 供給電圧(UN) 線ありの非保護多芯ケーブルで最大達成可能なDC

| FMレベル | 信号評価 |

| 同極性 | |

| 1 | None |

| 2 | None |

| 3 | None |

分析: 表J.3 と比較すると、全体的に達成可能なDC が低下しています。この理由は、新たな故障モードの追加にあります。ケーブル内に電源線(UN) が存在することで、「安全信号線と電源線との短絡」という、より検出が困難な故障が発生する確率が考慮されるためです。この種の故障は単純な監視ロジックでは検出しにくいため、DC が全体的に引き下げられています。

表J.5:リスクの低減 – 保護されたケーブル

表J.5 供給電圧(UN) 線の有無にかかわらず保護された多芯ケーブルで最大達成可能なDC

| FMレベル | 信号評価 |

| 同極性 | |

| 1 | Medium |

| 2 | Low |

| 3 | None |

分析: この表では、DC がJ.3 およびJ.4 と比較して大幅に改善されています。この劇的な改善の背景には、「故障除外(Fault Exclusion)」という重要な原則があります。ケーブルがケーブルダクトや外装ケーブルなどによって物理的に保護されている場合、設計者は「ケーブルの破断や圧壊による短絡」といった特定の物理的故障の発生確率が無視できるほど低いと見なし、その故障モードを評価から「除外」することが許されます 。この正当性は、関連規格であるISO 13849-2 の表D.4 を参照することで担保されています 。

あわせて読みたい

「故障除外」をわかりやすく解説:ISO 13849-1, ISO 13849-2, ISO 14119 から紐解く機械安全の設計にお…

みなさん、こんにちは。ジュンイチロウです。 お久しぶり! 今回は、意外と知られていそうで、実は良くわからない「故障除外」について解説いたします。 最近、故障除外…

故障が「除外」されると、DC の計算式

$$DC=\frac{検出された危険側故障率} {全危険側故障率}$$

の分母である「全危険側故障率」が小さくなります。その結果、DCの値は向上します。

したがって、表J.5 と他の表との違いは、電子的な診断技術の差ではなく、ケーブルの物理的な保護という機械的設計の選択が、安全インテグリティの計算値に直接的かつ定量的な影響を与えることを示しています。これは、安全規格群が相互に連携していることを示す好例です。

以下の表は、ISO 14119 の表J.3, J.4, J.5 のロジックを統合し、設計者が実用的な判断を下すための指針としてまとめたものです。

スクロールできます

| 配置 | 配線 | 信号評価 | FM = 3 | FM = 2 | FM = 1 |

| 単一配置 | ブランチ/スター | 静的(同極性/逆極性) | None | Low | Medium |

| 動的信号 | Low | Medium | Medium | ||

| ループ | 静的(同極性/逆極性) | None | Low | Medium | |

| 動的信号 | Medium | Medium | Medium | ||

| 冗長配置 | ブランチ/スター | 静的(同極性/逆極性) | None | Low | Medium |

| 動的信号 | Low | Medium | Medium | ||

| ループ | 静的(同極性) | None | Low | Medium | |

| 動的信号 | Medium | Medium | Medium |

信号評価と高度な故障検出

表J.3, J.4, J.5 の列に示されている「信号評価」は、安全コントローラが入力信号をどのように解釈し、故障を検出するかの技術的な違いを表しています。

基本的な評価:同極性と逆極性

これらは、2チャネルの冗長信号を評価する基本的な方法です 。

同極性 (Same Polarity)

2つのチャネルが共にON(例:24V)またはOFF(例:0V)になることを期待します。

逆極性 (Inverse Polarity)

1つのチャネルがON(24V)のとき、もう一方はOFF(0V)になることを期待します。逆極性は、チャネル間の短絡(クロスショート)を検出しやすいため、同極性よりもわずかに高いDC を提供することが表から読み取れます。

高度な評価:動的信号(テストパルス)のメカニズム

表の中で「動的信号」が一貫して最も高いDC を達成できる理由は、その高度な故障検出メカニズムにあります。

動的信号とは、一般的に「テストパルス」として知られ、安全なON 状態(通常24V)の信号に、周期的で非常に短いOFF パルスを重畳させたものです。安全コントローラは、この特定のパルスパターンが存在することを確認して、回路の健全性を監視します。

故障検出ロジック 電源への短絡(24Vショート)

信号線が外部の定常的な24V 電源に短絡すると、周期的なOFF パルスが「かき消され」てしまいます。コントローラは電圧がパルス状に低下することを期待していますが、それが観測されないため、短絡故障を検出できます 。

チャネル間短絡(クロスショート)

2つの安全チャネル(OSSD1 と OSSD2)のテストパルスは、意図的に非同期または時間的にずらして生成されます 。もしチャネル1 の入力でチャネル2 用のパルスパターンが検出された場合、コントローラはクロスショートが発生したと判断します。

断線

断線は恒久的なOFF 状態となり、本質的に検出されます。

ここで、しばしば見過ごされがちな重要な技術的詳細があります。それは、テストパルスがどこで生成されるかという点です。

安全入力側での生成

一部のシステムでは、安全入力モジュールがテストパルスを生成し、機械式スイッチのような受動的な(パッシブな)デバイスの配線診断を行います 。

デバイス側での生成 (OSSD)(Output Signal Switching Device)

ライトカーテンやRFID スイッチのような、より高度な安全機器は OSSD 出力を持ち、これらは自己監視のために自身の内部でテストパルスを生成します 。この場合、配線の診断責任は安全入力モジュールから OSSD 機器自体に移ります。

この違いは、致命的な設定ミスにつながる可能性があります。自己診断機能を持つ OSSD 機器を、テストパルスを生成する設定になっている安全入力に接続すると、二つのパルスが干渉し、システムはこれを故障と誤認して停止します 。

したがって、OSSD 機器を使用する際は、接続先の安全入力を「パッシブ」に設定、すなわちテストパルス生成機能を無効にする必要があります。附属書J の表にある「動的信号」という表記は、その原理を指しますが、実際の適用においては、使用するハードウェアの仕様に合わせた正しい設定が不可欠です。

技術的解決策:フォールトマスキングへの効果的な対策

このセクションでは、単純ですがコストのかかる解決策から、最新の先進的な解決策まで、進化の道のりに沿って対策を構造化します。

1. 根本的(力技)解決策:個別配線

メカニズム

各インターロック装置(または小規模なローカルグループ)を、安全PLC またはセーフティリレーの専用の2チャンネル入力に個別に配線します。

有効な理由

このアーキテクチャは、ロジックユニットが各装置の状態を独立して監視できるため、あるスイッチが別のスイッチをマスキングする可能性を完全に排除します。故障は単一の入力に分離されます。

長所と短所

最高の安全インテグリティと単純な診断が可能です。一方で、配線、盤内スペース、I/O 点数の面で非常に高いコストがかかります。

2. デバイスレベルの解決策:OSSD 出力付き自己監視型スイッチ

直列接続におけるフォールトマスキングを回避するための現代的な業界標準です。自己監視機能を持つ OSSD 出力を備えた装置(例:RFID スイッチ、ライトカーテン)は、コンポーネントレベルで問題を解決します 。これらの装置は高い内部診断カバレッジ(多くの場合 DC≥99%)を持つため、自身の故障や配線異常を検知すると自律的に出力をOFF にし、危険な状況を防ぎます。

これにより、直列上の他の装置の状態にかかわらず安全が確保されるため、附属書J のフォールトマスキング確率の分析そのものが不要になります。

メカニズム

無電圧接点の代わりに、自己監視型の半導体出力である OSSD 出力を備えた安全スイッチを使用します。

OSSD テストパルスの詳細な技術解説

OSSD がどのように機能するかの技術的な詳細を以下に示します。

2つの OSSD 出力(OSSD1, OSSD2)は、静的な 24V ではありません。

ON状態において、各チャンネルは周期的に出力が 0V に落ちる非常に短い「テストパルス」を送信します。

これらのパルスは OSSD1 と OSSD2 間で非同期(位相がずれている)です。

装置内部のマイクロプロセッサが自身の出力を監視します。テストパルスを指令したにもかかわらず出力電圧が低下しない場合、24V への短絡を検出します。

受信側の安全PLC/リレーは、これらの短いパルスをフィルタリングして一定の ON 信号として認識するように設計されています。チャンネル間で不一致(例:一方が ON、他方が OFF)を検出した場合、OSSD 配線間の短絡(クロスサーキット)を検出できます。

有効な理由

故障検出機能が中央のコントローラから個々のデバイスに移されます。故障したスイッチは自身の故障を検出し、自身の出力を確実に遮断するため、直列内の他のスイッチの動作状況に関わらず、安全状態を確実に信号化します。これにより、他のデバイスによるフォールトマスキングが不可能になります。

長所と短所:

直列接続で最高のPL (PLe) を達成可能です。配線の簡素さを維持できます。機械式スイッチよりも初期の部品コストが高くなります。

最初からTYPE4 OSSD付にしとけばいいかもしれませんね!

3. システムレベルの解決策:診断機能を持つ安全ネットワーク

メカニズム

デバイスが単一ケーブル上で直列に接続されますが、マスター/ゲートウェイとデジタル通信を行う専用の安全ネットワークまたはバスシステムを使用します。例として、 シュメアザール社 SD-Interface などが挙げられます。

有効な理由

これは単純な電気的直列回路ではなく、通信ネットワークです。マスターユニットはバス上の各デバイスに個別に状態を問い合わせます。これにより、「扉 A1 が開いています」「扉 B2 に内部故障あり」「扉 C3 の位置がずれています」といった豊富な診断データを受信します。各デバイスの状態が個別に明確に把握できるため、フォールトマスキングは不可能です。

長所と短所

配線の簡素さと、トラブルシューティングおよびダウンタイムを大幅に削減する比類なき診断情報を組み合わせた究極の解決策です。初期コストが最も高くなります。特定の製造者のアプリケーションに依存する場合があります。

スクロールできます

| 対策 | 安全インテグリティ (PL/DC) | 配線コスト/複雑性 | 部品コスト | 診断能力 | トラブルシューティング時間 |

| 個別配線 | 最高 | 非常に高い | 低い(リレー/PLCによる) | 高い(故障箇所特定が容易) | 短い |

| OSSDデバイス | 最高 (PLe) | 低い | 中程度 | 中程度(故障デバイスは特定可能) | 中程度 |

| 診断機能を持つネットワーク | 最高 (PLe) | 非常に低い | 高い | 最高(故障内容まで特定可能) | 最短 |

この表は、設計者が用途のニーズに応じてコスト、複雑性、性能のトレードオフを比較検討するための明確な意思決定フレームワークを提供します。

結論:想定された安全から検証されたインテグリティへ

主要な所見の要約

本稿の結論として、以下の重要な点を要約します。

- 無電圧接点を持つインターロック装置の直列配線において、フォールトマスキングは現実的かつ深刻な危険です。

- それは診断カバレッジ(DC) を直接的に低下させ、システムの実際のパフォーマンスレベルが計算上のPL よりも低くなる原因となります。

- ISO 14119 附属書J は、この低下を評価するための必須の枠組みを提供します。

ベストプラクティスのための実践的提言

- 決して想定に頼らない: カテゴリ2 以上を要求するシステムにおいて、ISO 14119 附属書J に準拠した正式なフォールトマスキング分析なしに、直列回路が要求 PLr を満たしていると決して想定してはいけません。

- インテグリティを考慮した設計: PLd 以上を要求する新しい機械では、OSSD 出力付きのインターロック装置または診断機能を持つネットワークを使用することをデフォルトのベストプラクティスとすべきです。個別配線も有効な選択肢ですが、コストが高くなります。

- 既存システムの監査: 直列配線された機械式スイッチを持つ既存の機械は、監査の対象としなければなりません。附属書J の手法を用いて、実際に達成可能な PL が、元のリスクアセスメントで定められた PLr を依然として満たしているかを確認する必要があります。改善措置が必要となる場合もあります。

- すべてを文書化する: 選択した手法(簡易または通常)、すべての入力パラメータ(頻度、オペレーター数)、そして最終的な DC の決定を含むフォールトマスキング分析は、機械の技術文書の正式な一部としなければなりません。

SO 14119 附属書J の表J.3、J.4、J.5は、ケーブルの物理的保護(保護の有無)と内部の電源線の有無という、配線に起因する故障確率の違いを反映した、リスクの階層構造を示しています。表J.5が最も高いDC を許容するのは、物理的な保護によって「故障除外」が適用できるためであり、表J.4 が最も低いのは、内部電源線との短絡という新たな故障モードが加わるためです。

しかし、附属書J の存在自体が、機能安全の専門家にとって重要な示唆を与えています。それは、この附属書が、本質的にリスクを伴う設計を評価・正当化するためのツールであるという事実です。

最高の安全性を追求する上での最終的な目標は、附属書Jの表を巧みに適用することではなく、より優れた設計アプローチ、すなわち OSSD 出力付きデバイスの活用や診断機能付きセーフティバスの導入によって、フォールトマスキングという問題そのものを設計段階から排除することです 。

これらの現代的なソリューションは、直列接続においても最高のパフォーマンスレベルであるPLe の達成を可能にし 、附属書J の評価ではPLd に制限されるという制約を乗り越えさせます 。

ここまでお読みいただきありがとうございました。機械安全専門家の役割は、規則を適用するだけでなく、問題を根本から解決する技術を選択し、安全かつ効率的なシステムを構築することにあると思います。

この記事が皆様のお役にたてれば幸いです。